# A Fault Tolerant Pipelined Double Precision Reversible Floating Point Adder/Subtract or in FPGA

F.Mhaboobkhan,Assistant

Professor DepartmentofECE P.A.CollegeofEngineeringandTechnologyPollachi,Coimbatore khanmhaboob@gmail.com

> Dr. R. P MeenaakshiSundhari, Professor, Department of ECE, P. A. College of Engineering and Technology, Pollachi, Coimbatore, <u>rpmeenaakshi@gmail.com</u>

Abstract:Inrealworldcomputation, there are two methodologies by which numbers can be stored they arefixed point notation and floating point notation. Floatingpoint operations are used to a greater extent in most of the computational devices. Frequently used operation is Floating point addition and Subtraction. In Applicationssuch as, Digital Signal Processing and Optical computingSpeed of operation and low power consumptions are themajor criteria. Reversible logic provides solution for thisproblem.InthispaperaDoubleprecisionPipelinedReversiblefloatingpointadder/subtractor(RFP A)isdesignedusingKMDgates.TheRFPAhasReversibleConditionalswapping,Reversibleadder,Re versibleNormalization and Reversible round off blocks in it. TheDesigned RFPA is coded using Verilog and the same hasbeen simulated using Modelsim 10.7c. Parameters such asMaximum operation frequencyand logiccellutilizationarecalculatedusingQuartusPrimeedition20.2using10CX220YF672I5G device with respect to Cyclone 10 GX family. The results has been compared between Single precision and Double precision RFPA which shows thatDouble precision RFPA has greater operating speed by afactorof1.1 attheexpenseofhigherlogiccellutilization.

# Keywords: Reversible logic, RFPA, Maximum operating frequency.

# I. INTRODUCTION

The roadmap for the semiconductors has predicted beyond thenanotechnology it is highly impossible to shrink the devices.Even if the devices are shrunk it may lead to second ordereffects.Anewtechnologymustbeevolvedtokeepthemoore'slawalive.[1,2].Landauerprovedtha t,anyirreversible or conventional computation will dissipate KTln2Joules (k is Boltzmann's constant and T is the temperature) ofheatsinceitlosesbitinformationfromin-puttooutputtransition[3].Reversiblelogicisbasedononetoonemapping. A reversible logic circuit has an equal number of outputs. The input of a reversible circuit can beuniquely identified from its output.[4]. Reversible logic canbe used to prevent the loss of information during

operations and also used in the emerging technologies like Quantum Computing, Quantum Dot Cellular Automata and Digital

Signal Processing [5]. This fault tolerant /detection approachcan beaccomplishedby parity-preservinggates,wheretheinputparityisequal to the outputparity[6].

The arithmetic operation that is performed in most of the DSPprocessorsmakesuseoffloatingpointoperations.Mostwidely used representation of

http://annalsofrscb.ro

floating point numbers is IEEE754standardrepresentation. This represented are of two types.

- 1. SinglePrecisionRepresentation

- 2. DoublePrecisionRepresentation.

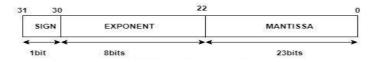

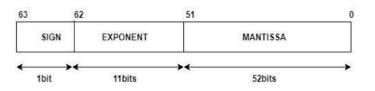

Figure1and2showstherepresentationofboththeformats.

### Fig.1.IEEE754singleprecisionfloatingpoint Dataformat

#### Fig.2.IEEE754DoubleprecisionfloatingpointDataformat

In single precision, there are 32 bits, the MSB bit is sign bit,8 bits are exponent and the last 23 bits are mantissaIn doubleprecision, there are 64bits, the MSBbit is sign bit, next11bits are exponent and the last 52 bits aremantissa. The bitrange of floating point values are described in Table-I. The bias value for Double Precision Floating Point is 1023.

#### TABLE I. BITRANGEOFFLOATINGPOINTVALUES

| Precisio<br>n | SignBi<br>t | Exponent  | Mantissa   |

|---------------|-------------|-----------|------------|

| Single        | 1(31)       | 8 (30-23) | 23(22-00)  |

| Double        | 1(63)       | 11(62-52) | 52 (51-00) |

The paper is structured as follows; Section II reviews a fewreversible logic primitives. Section III explains the reversiblegateusedinthisproposedarchitecture.SectionIVbrieflyoutlines the floating point adder architecture and gives detailsabout its major reversible components. Section V discusses theresultsandSectionVIconcludesthepaperfollowedbyreferences.

#### II. REVERSIBLELOGICPRIMITIVES

The logic gates that are generally used (AND, OR, NAND,NOR, XOR and XNOR) are irreversible [3].Reversible gatessuch as Feynman, Toffoli, Peres, Fredkin, HNG and TSG aredeveloped by the researchers.These gates are defined by theirnumber of inputs and outputs.

A. Quantumcost:

The number of  $1 \times 1$  and  $2 \times 2$  reversible gates or quantum ates required in the architecture is known as the quantum cost of the reversible gate. The quantum costs of all reversible  $1 \times 1$  and  $2 \times 2$  gates are taken as unity[7].

*B.* Garbageoutputs:

The unusedoutputs foundin reversible circuits are knownasgarbage outputs[6].

C. LogicalCalculations:

Logical calculations refer the total number of XOR( $\alpha$ ), AND( $\beta$ ) and NOT( $\gamma$ ) operations required to real ize the function [8].

| D. Re       | versibility: |   |                   |                       |                      |    |   |         |           |

|-------------|--------------|---|-------------------|-----------------------|----------------------|----|---|---------|-----------|

| The         | function     | f | (x <sub>1</sub> , | <b>x</b> <sub>2</sub> | <br>x <sub>n</sub> ) | of | n | Boolean | variables |

| http://anna | lsofrscb.ro  |   |                   |                       |                      |    |   |         | 2948      |

iscalledreversibleifthenumberofoutputsisequaltothenumberofinputsandanyinputpatternmapstoau niqueoutputpattern [9, 10].

#### E. Universality:

Areversible gate is said to be satisfying universality property only when it could be able to realize NOT, NAND /AND&NOR/OR functions [11].

#### *F. Fault-tolerance:*

$\label{eq:Fault-tolerance} Fault-tolerance is a method to preserve same parity between input and output vectors over one to one mapping of the reversible circuit [12-14]. The input and output vectors of any fault-tolerant gates are I_v {I_{n-1}, I_{n-2}, \ldots I_0} and O_v {O_{n-1, On-2}, \ldots O_0} where the following must be preserved$

$I_{n\text{-}1} \bigoplus I_{n\text{-}2} \bigoplus \ldots \bigoplus I_0 = O_{n\text{-}1} \bigoplus O_{n\text{-}2} \bigoplus \ldots O_0$

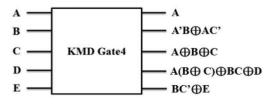

### III. PROPOSEDREVERSIBLEGATE

#### A.KMDGate 4:

The reversible gates used in this paper are KMD gate. KMD is a  $5\times5$  parity preserving reversible gate. This gate is also anoutput. Figure 3 shows the general structure of KMD gate 4.

#### Fig.3KMDGate 4

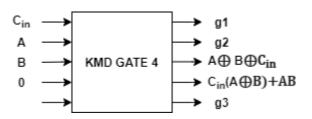

A single KMD Gate 4 can be used as a full adder. Out oftheavailable5inputs,4inputshavetobeusedtomakea

KMDgatetoworkasa1bitfulladder.ThestructureoftheKMDgate asafulladder isshowninthefigure4.

#### Fig.4KMDgateasaFull Adder

#### IV. FLOATINGPOINTADDER/SUBTRACTOR

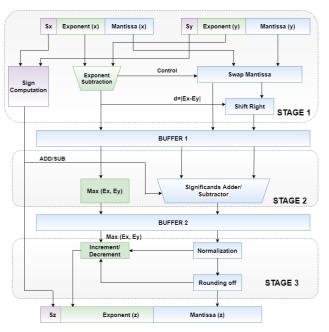

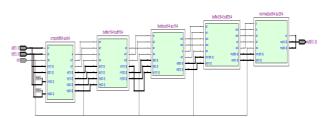

The procedure for adding/ subtracting two floating pointnumbersinIEEE754DoubleprecisionformatconsistofThree major steps.Figure 5 shows the Pipelined ArchitectureofRFPA.

Fig.5PipelinedReversiblefloatingpoint Adder/Subtractor(RFPA)

Two Double precision floating point numbers are fed as theinput in IEEE 754 standard. Each number contains a Sign bit,11 bit Exponent and a 52 bit Mantissa. There are 3 stages ofcompution, which in a buffer is added at the end of each stagetosupportpipelining.Inthefirststagetwoexponentsaresubtracted to check which among them is smaller. The smallerexponent is incremented unitl it aligns with the larger. Uponincrementing the exponent, the mantissa of smaller exponentis shifted right toalign with the smaller exponent without altering its value. In these condstage the Significands areadded Reversible third using KMD adder. In the stage the sumisnormalized and rounded off toget the desired value. Figure 5 illustrates Pipelined the Architecture of Reversible floatingpointadder/subtrator.

#### A. Reversible Compareand Shiftunit

Architecture The first of the is Compare stage and Shiftoperation. The exponents of the two floating point numbers are subtracted. The minuendistwo' scomplemented and the difference is calculated. In this Paper, an 11 bit 2's complement Reversible E xponentSubtractorisproposedbasedonKMDgate4.TheMSBbitoftheExponentsubtractor acts as the control input to the swap mantissa block. If Exponent(X) > Exponent(Y) the positions of their mantissaare retained as it is, if not the positions are swapped before passing the same to next stage. Once they are swapped, for he rest of the computation process it is assumed that floatingpoint number X has greater exponent compared to Y.Themagnitude of the Exponent subtractor contains the amount bywhichtheMantissaofthesmallerexponentmustbeshifted.

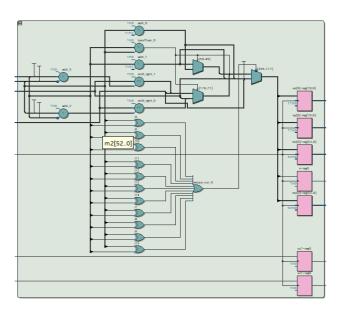

Once the difference is extracted it is presented as the inputto Shift Right block in which the Mantissa (Y) is shifted bydesiredvalue.TheFigure6Show theRTL schematicofCompareandShiftblock.

#### Fig.6.RTLSchematicofCompareandShiftblock

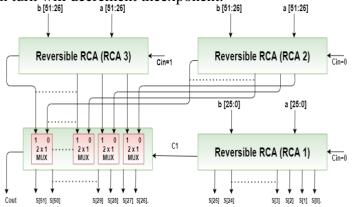

#### B. ReversibleAdder/SubtractorUnit

In order to perform the mantissa addition/subtraction a 52bit carry select adder has been designed using KMD gate 4.The52bitCarryselectadderconsistsofthreeseparateReversible Ripple carry adder (RCA). The first lower order 26bits is taken and given as the input to 26 bit RCA (RCA1) andthe lower order sum ranging from [25:0] is generated alongwith an output carry (C1). This Higher order bits from [51:26]is given as the inputs to two separate RCA (RCA2 and RCA3)with each having its initial carry as 0 and 1 respectively. Thesum and carry results from RCA2 and RCA3 are multiplexedand selected based on the output carry (C1) generated fromRCA1. The structure of a 52 bit Carry select adder is shown infigure7.

#### C. ReversibleNormalizationunit and Roundingoff

The third stage of the RFPA is Normalization and roundingunit. The normalization step could be a left shift or a right shift the mantissa. If the left shift is required for normalizationthenleadingzerosmustbecountedbasedonwhichtheshifting will be carried out which in turn will decrement the exponent.

#### Fig.7 ReversibleCarrySelectAdder

Similarly if theright shift isrequiredfornormalizationthenthenormalizationunitshiftsthemantissabysingleposition which in turn will increment the exponent. This stepensures correct value of mantissa and exponent. Finally theroundingoffunitroundsofthemantissabasedonzeroroundingalgorithms.

### v. RESULTSANDDISCUSSION

ThePipelinedDoublePrecisionRFPAisdesignedandsimulated using Modelsim 10.7c.Parameters such as Power,Cell utilization, Timing and Maximum Operating FrequencyareanalyzedusingQuartusPrimeEdition20.2,10CX220YF672I5G device with respect to Cyclone 10 GXfamily.

# A. SIMULATIONOFPIPELINEDRFPA

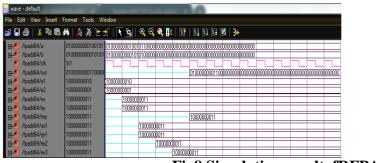

Fig8.Simulation resultof RFPA as adder

The Simulation result of Pipelined RFPA as an adder is shownin theFig8. The Inputsfor the adderare +10.75and5.25given indoubleprecisionformat. The result obtained has been +16.

| File     Edit     View     Insett     Format     Tools     Window       Image: State | 😹 wave - default        | -                 | 0             |            | -       |          |         |         |                    |         |         |         |         |         |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|---------------|------------|---------|----------|---------|---------|--------------------|---------|---------|---------|---------|---------|--------|

| B→     /hpad54/a     0100000000001     0100000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | File Edit View Insert F | ormat Tools Wi    | indow         |            |         |          |         |         |                    |         |         |         |         |         |        |

| B     Apad54/b     Difficult11111100     Difficult1111100     Difficult1111100       0     Apad54/stal     Difficult1111100     Difficult111100     Difficult1111100       0     Apad54/stal     Difficult111111100     Difficult11111100     Difficult11111100       0     Apad54/stal     Difficult111111100     Difficult11111100     Difficult11111100       0     Apad54/stal     Difficult11111110     Difficult111111100     Difficult11111100       0     Apad54/stal     Difficult1111111110     Difficult111111100     Difficult11111100       0     Apad54/stal     Difficult1111111111110     Difficult11111111100     Difficult111111100       0     Apad54/stal     Difficult111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 🖆 🗄 🍯 👗 🖣 🛍 (           | M   占 🔏 1± :      | ¥ 🖹 🖳         | ତ୍ତ୍ର ତ୍ର୍ | ۹ 🗗     | 1        | 1       | î 💵 I   | š   3 <del>.</del> |         |         |         |         |         |        |

| Apad54/ak St1 Apad54/ak St1 O Apad54/ak D Apad54/ak St1 O D Apad54/ak D D Apad54/ak D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ⊞- <b>4)</b> /(padd64/a | 0100000000000011  | 010000000000  | 001110000  | 0000000 | 00000000 | 0000000 | 0000000 | 0000000            | 0000000 |         |         |         |         |        |

| g.s     Apad54/or     00111111110010     0011111111001000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ⊞-• //padd64/b          | 10111111111111100 | 1011111111111 | 110000000  | 0000000 | 00000000 | 0000000 | 0000000 | 0000000            | 0000000 |         |         |         |         |        |

| m ≠     /hpad54/e1     100000000     100000000     100000000     100000000     100000000     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001     1000000001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 🌖 //padd64/clk          | St1               |               |            |         |          |         |         |                    |         |         |         |         |         |        |

| B→     /hpad54/e2     011111111     0     0     0       B→     /hpad54/ex     010000001     100000001     0     0       B→     /hpad54/ex     100000001     000000001     0     0       B→     /hpad54/ex     100000001     0     0     0       B→     /hpad54/ex     1000000001     0     0     0       B→     /hpad54/ex     100000001     0     0     0       B→     /hpad54/ex1     1000000001     0     0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ⊞-•● //padd64/out       | 0011111111100110  |               | _          |         |          | 0011111 | 1111001 | 1000000            | 0000000 | 0000000 | 0000000 | 0000000 | 0000000 | 000000 |

| p→     //pad64/ex     100000001     100000001     0       p→     /pad64/ey     1000000001     00000001     0       p→     /pad64/ey     1000000001     0000111111110     0       p→     /pad64/ey     1000000001     0000101     0       p→     /pad64/ey1     1000000001     00000001     0       p→     /pad64/ey1     1000000001     000000001     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ⊞-4) /fpadd64/e1        | 1000000000        | 10000000000   |            |         |          |         |         |                    |         |         |         |         |         |        |

| Br∮ /hpad54/ey 1000000001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         | 0111111111        | 011111111111  |            |         |          |         |         |                    |         |         |         |         |         |        |

| Br∮ Apad5A/eyr 011111110 011111110 0111111110 01111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ⊞ /fpadd64/ex           | 10000000001       | 10000         | 1000001    |         |          |         |         |                    |         |         |         |         |         |        |

| Be∮ //pad68//e/1 1000000001 1000000001 000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ⊞ /fpadd64/ey           | 10000000001       | 10000         | 1000001    |         |          |         |         |                    |         |         |         |         |         |        |

| m=∮ //psd64/ey1 1000000001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ⊞-🌖 /fpadd64/exy        | 01111111110       |               | _          |         |          | 0111111 | 1110    |                    |         |         |         |         |         |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ⊞-� /fpadd64/ex1        | 10000000001       |               | 1000000    | 0001    |          |         |         |                    |         |         |         |         |         |        |

| m 4 //padd64/ex2 1000000001 (10000000001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ⊞-🌖 /fpadd64/ey1        | 10000000001       |               | 1000000    | 0001    |          |         |         |                    |         |         |         |         |         |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ⊞-� /fpadd64/ex2        | 10000000001       |               | _          | 100000  | 0001     |         |         |                    |         |         |         |         |         |        |

| m_//pad64/ex3 1000000001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ⊞-� /fpadd64/ex3        | 10000000001       |               | _          |         | 1000000  | 0001    |         |                    |         |         |         |         |         |        |

**Fig.9.SimulationresultofRFPAasSubtractor** The Simulation result of Pipelined RFPA as a Subtractor isshownintheFig9.TheInputsforthesubtractorare2.4375and-1.75givenindoubleprecisionformat.Theresultobtained hasbeen+0.6875.

B. RTLVIEWEROFRFPA

#### Fig.10RTLschematicofRFPA

The RTL schematic of Pipelined RFPA is shown in Fig 10after the post layout simulation. It can be seen in the there arethreemajorblocksnamelyReversibleCompareandShift,ReversibleFloatingpointadder/subtracto randReversibleNormalizationandroundingoffseparatedbybufferstoperformPipelining.

#### C. CHIPPLANNERVIEW

http://annalsofrscb.ro

# TheChipPlannergives the visual display of chipresources.

# Fig.11ChipPlanner Viewof RFPA

Fig 11 is the view of RFPA in chip planner in which it showslogic placement, logic Block regions, resource usage, routinginformation, fan-ins and fan-outs, paths between registers, and high-speed transceiver channels.

### D. POWERANALYSISSUMMARY

TheTableIIshowsthecomparativestudyofpowerutilizationbetweenSinglePrecisionRFPA andDo ublePrecision RPFA. It can be seen from the table that the totalpower dissipation has increased by 4.3% in Double PrecisionRFPA. Fig. 12 shows the graphical representation of DesignedRFPA architecture.ThegraphshowsthatSingleprecisionRFPA dissipates lesser power compared to Double precisionRFPAbecauseofthefactthat,duetoincreaseinthenumberof bits the switching activity (Dynamic power) of latter alsogets increased which in turn contributes to the total powerdissipation.

| PowerAnal<br>ysis                       | Single<br>Precis<br>ion<br>(m<br>W) | Doubl<br>ePrec<br>ision<br>(mW) | %of<br>Dissipation |      |        |      |

|-----------------------------------------|-------------------------------------|---------------------------------|--------------------|------|--------|------|

| Static<br>PowerD<br>issipatio<br>n      | 1.71                                | 4.73                            | 63.84%             |      |        |      |

| Dynamic<br>PowerDiss<br>ipation         | 5.82                                | 9.21                            | 36.8%              |      |        |      |

| Core<br>DynamicPo<br>werDissipat<br>ion | 25.7<br>9                           | 51.97                           | 50.37%             | _    |        |      |

|                                         |                                     |                                 | Total<br>PowerD    | 639. | 668.26 | 4.3% |

### TABLE II. POWERANALYSIS

Fig.12Powerutilization of RFPA

### E. UTILIZATIONSUMMARY

The Table III shows the Comparative study of Single Precision RFPA and Double PrecisionPrecisionRFPAwithrespectto hardware utilization whereas Fig13 shows the graphical representation of the same.respect

| Paramet<br>ers           | Singl<br>ePreci<br>sion   | Doubl<br>ePreci<br>sion | %<br>ofUtiliz<br>ation |

|--------------------------|---------------------------|-------------------------|------------------------|

| Logic<br>utilizati<br>on | 596                       | 2,04<br>2               | 71%                    |

| Tota<br>lregist<br>ers   | 265                       | 513                     | 48.3<br>%              |

| Total<br>pins            | 97<br>596<br>Logic utiliz | 193                     | 49.7<br>%              |

TABLE III. AREAUTILIZATION

#### Fig.13ComparisonofUtilizationSummary

ThetablelisttheparameterscomparedforhardwareutilizationsuchasLogiccell,Registersandtotalpin s.ComparingwithSinglePrecisionRFPA,DoubleprecisionRFPAutilizesmorenumberoflogicblocks, Registerandrequires as much as double the number of pins for input andoutputby71%,48.3% and49.7% respectively.

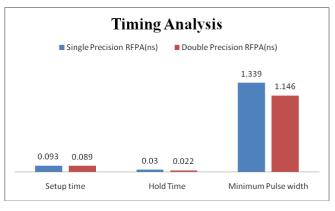

### F. STATICTIMINGANALYSIS

| Static<br>Timi<br>ngAn<br>alysis | Single<br>Precision<br>(ns) | Double<br>Precision<br>(ns) | %<br>ofImprov<br>ement |

|----------------------------------|-----------------------------|-----------------------------|------------------------|

| Setuptim<br>e                    | 0.09<br>3                   | 0.089                       | 4.3%                   |

| HoldTim<br>e                     | 0.03<br>0                   | 0.022                       | 26.66<br>%             |

| Minim<br>umPu<br>lsewi<br>dth    | 1.33<br>9                   | 1.146                       | 14.4<br>%              |

TABLE IV. TIMINGANALYSIS

The Table IV shows the comparative Static timing analysisforSingleprecisionRFPA and DoubleprecisionRFPA whereas

#### Fig.14ComparisonofTimingAnalysis

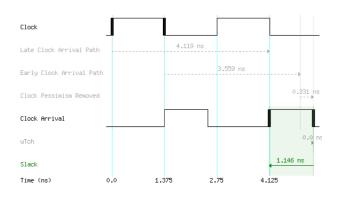

The Fig 15 shows the Graphical representation of Minimumpulsewidth required for designed Pipelined RFPA.Fig 14shows the graphical representation of the same. The setup time is the minimum amount of time before the active edge of the clock that the data should be stable. Similarly, Hold time is defined as the minimum amount of time after the clock's active edge during which data must be stable. From the graphit can be seen that there is considerably improvement in setuptime, hold time and Minimum pulse width by 4.3%, 26.66% and 14.4% respectively.

### Fig.15GraphicalrepresentationofMinimumPulseWidth

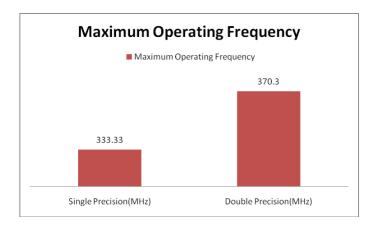

TABLEV. MAXIMUMOPERATINGFREQUENCY

### G. MAXIMUMOPERATINGFREQUENCY

| Paramete                              | SinglePr     | DoublePr     |

|---------------------------------------|--------------|--------------|

| r                                     | ecision(MHz) | ecision(MHz) |

| Maximu<br>mOpera<br>tingFreq<br>uency | 333.33       | 370.<br>3    |

The Table V shows the comparative study of Maximum operating frequency Single Precision RFPA and Double Precision RFPA whereas Fig16 shows the graphical representation of the same. The graphical representation shows that the maximum operating frequency of Double precision RFPA has increased by a factor of 1.1 compared with Single precision RFPA.

# Fig. 16 Comparison of Maximum Operating Frequency in differenttechnologies

# VI. CONCLUSION

Speed of Operation and area reduction is perhaps the majorconcern in most of the DSP applications. This paper presentsaPipelinedRFPMwhichusesIEEE754standard.AllmodulesofpipelinedRFPMhavebee

http://annalsofrscb.ro

ndesignedandsimulatedusingModelsim10.7c.Theparameterssuchasarea,power,cellsutilizatio nandmaximumoperatingfrequencyhasbeenanalyzedusingcadencegenussynthesis 14.25 on 180nm and 90nm technology,in which PipelinedRFPM with 90nm technology shows better improvement intermsofArea,Cellsoccupiedby67.17% and 4.42% respectively while Maximum operating frequency by a factor of 2.73. The designed RFPM can be used for High

#### REFERENCES

speed DSPapplicationssuchasFastFourierTransform,QuantumComputingandOptical Computing

- [1] Internationaltechnologyroadmapofsemiconductor2.0,EditionExecutiveRe-port.2015

- [2] https://spectrum.ieee.org/semiconductors/devices/transistors-could-stop-shrinking-in-2021.

- [3] A.Prasanth, S.Jayachitra, 'A Novel Multi-Objective Optimization Strategy for Enhancing Quality of Service in IoT enabled WSN Applications', Peer-to-Peer Networking and Applications, Vol.13, 2020, pp.1905–1920.

- [4] MichealNachtigal, "Design of Reversible Floating PointAdder Architecture", 11<sup>th</sup> IEEE International ConferenceinNanotechnology, 2011.

- [5] A.Kamaraj,P.Marichamy,M.Nagalakshmi@Subraja,"DesignandImplementationofFloatingPo intMultiplierinReversibleLogicwithNovelGates",InternationalConference on Innovations in Engineering and Technology(ICIET),2016.

- [6] Jaichandran R, BagathBasha C, Shunmuganathan K.L, S. Kanaga Suba Raja 'Sentiment Analysis of Movies on Social Media using R Studio', International Journal of Engineering and Advanced Technology, ISSN: 2249 8958, Volume 8, Issue 6, pp. 2171-2175,2019.

- [7] Jenil Jain, Rahul Agrawal, "Design AndDevelopment of Efficient Reversible FloatingPointArithmeticUnit", FifthInternationalConferenceonCommunication Systems andNetworkTechnologies, 2015

- [8] MojtabaValinataj ,MahboobehMirshekar , HamidJazayeri, Novel low-cost and fault-tolerant reversiblelogic adders, Comput. Electr. Eng. J. 53 (2016)56–72.

- [9] D. Maslov, Reversible logic synthesis, TheFaculty of Computer Science, The University of NewBrunswick, 2003.

- [10]D. Maslov, G.W. Dueck, Garbage in reversibledesigns of multiple output functions, in:Proceedings of the 6th International Symposium onRepresentations and Methodology of FutureComputing Technologies (RM 2003), Germany, Trier, March2003, pp.162–170.

- [11] Kalyan S. Perumalla, "Introduction to Reversible Computing, CRC Press, USA, 2014.

- [12] A.Prasanth, 'Certain Investigations on Energy-Efficient Fault Detection and Recovery Management in Underwater Wireless Sensor Networks', Journal of Circuits, Systems, and Computers, Vol. 30, 2020

- [13] A.Prasanth, S.Pavalarajan, 'Implementation of Efficient Intra- and Inter-Zone Routing for Extending Network Consistency in Wireless Sensor Networks', Journal of Circuits, Systems, and Computers, Vol.29, 2020

- [14] A.Prasanth, S.Pavalarajan 'Particle Swarm Optimization Algorithm Based Zone Head Selection in Wireless Sensor Networks', International Journal of Scientific & Technology Research, Vol.8, pp.1594-1597, 2019