# Implementation of Low Power AMBA-AHB Bus Utilizing the Multi-Coding Technique

## Prashant Mani<sup>1</sup>,K.Vijayan<sup>2</sup>, Pankaj Singh<sup>3</sup>, Abhishek Singhal<sup>4</sup>, Aaditya Agarwal<sup>5</sup>

Associate Professor<sup>1</sup>Assistant Professor<sup>2,3,4,5</sup> <sup>1,2,3,4,5</sup>SRM Institute of Science & Technology, Delhi-NCR Campus, India

**Abstract** – The objective of this paper is to diminish the intensity of Advanced Microcontroller Bus Architecture (AMBA-AHB). We have used a multi-coding technique for reducing the power of AMBA AHB. The primary driver of vitality dispersal is charging and discharging by transition activity. This paper describes the technique for reduction in power analyzed through a multi-coding technique. In this technique, the diminishing power dispersal is by minimal transition activity. This technical method is actualized with Verilog HDL programming. General execution is analyzed by using Model sim and Xilinx Tools.

Keyword: Encoder, Decoder, Master-Slave, System on chip, Swap data

#### 1. Introduction

Energy utilization is actual true angles in the arrangement of micro-electronic circuits [1]. As the advancement scales back to significant submicron innovation, the transport vitality lessening has turned out to be increasingly important [2]. On-chip transport correspondence design is one of the fundamental segments in a SOC stage. A proficient on-chip correspondence framework needs to fulfill the interface conduct of every IP piece incorporated inside the complex SOC [4]. This paper, discuss about bi levels, circuit/logic and algorithm with outline for diminishment of power. Diminishment of the power from first to last circuit and logic configuration to restrain power of various techniques at the circuit/rationale level can be utilized, for example

1. Power minimization through logic and device clock

(a) Minimize shifting activity utilizing logic operation;

(b) Optimize clock, transport stack.

(c) Smart circuit methods that reduced device test and inside swing.

2. Power minimization by way of algorithm and calculation

(a) Reducing the number of operations.

(b) Data coding (least moves to action).

### 2. Design method with AMBA-BUS

AMBA is universal widely accepted open SoC transport convention for predominant transports on minimum power consumptions. AMBA is a ideal interface detail that guarantees the similarity between various IP segments gave by various outline merchants. AMBA 2.0 determination characterizes three unique transports [3]:-

### 2.1 Advanced High-Performance Bus (AHB):-

AHB is utilized for address the obligation of high-performance synthesizable logic/circuits. AMBA-AHB is a modified and improved bus for the APB and apply the property of high clocking.

AHB transport is another era of AMBA-2.0 assurance which is planned to bring up the prerequisites of superior synthesizable outlines. AHB transport is an advanced system which is high above ASB and APB. The characteristics of AHB are a several bus masters, burst transfers, single-cycle bus master handover, single edge clock protocol, split transactions and large bus widths. A data section and address phase are the part of transaction in AHB. Only one bus master is available at a time. While as compared to superior excessive-performance Bus, the superior peripheral bus is only used to control access for low bandwidth. Despite, the APB has a cope with section and information section as like that of the AHB, it comes with a listing of low complexity sign. The components required for elite, high clock recurrence frameworks are asper the accompanying [3]:-

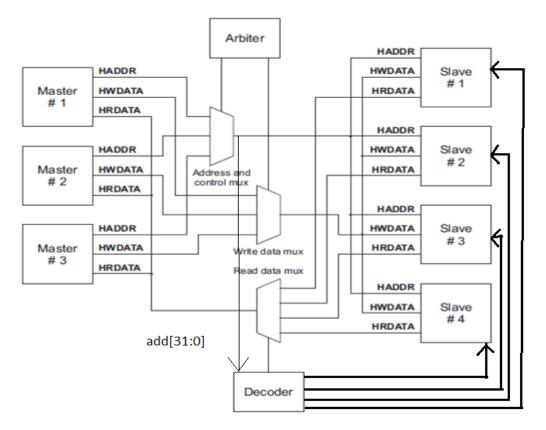

Fig 1 Working principle of AHB

- The Burst transfers (4/8/16 beat burst)

- Fractured transactions

- Handover of Bus master in a Mono cycle

- operation performed by Monoclock edge

- configuration of the data bus is Much wide (8 to 1024 bits)

- Stream Pipelined operation

### 2.1.1 Transport with AMBA AHB MASTER:

This transport ace can start, read and compose process by making utilization of an address & control data. Only a solitary transport ace at once is permitted to adequately utilize the transport.

### 2.1.2 Transport with AMBA AHB SLAVE:

This system responds to peruse and compose process Start by the master in a prescribed address range of space. Slave bus initiate signals to on the master regarding the results as a waiting, success or failure of the data transfer.

### 3 Transport with AMBA AHB Arbiter:

This transport decides and generates an arbitration that only a solitary transport ace at once is allowed to start the information transfers. Despite the way that the mediation plan is settled, any adjustment plan can be utilized like Round Robin, true Chance, fuzzy logic arbitration and depends upon the application prerequisite.

### 2.1.4 Transport with AMBA-AHB Decoder:

This transport is utilized to unspecific the address of every exchange and offer a select signal to the slave which included in transfer. A solitary brought together decoder is needed in each AHB executions.

### 3.0 Implementation of the Hardware

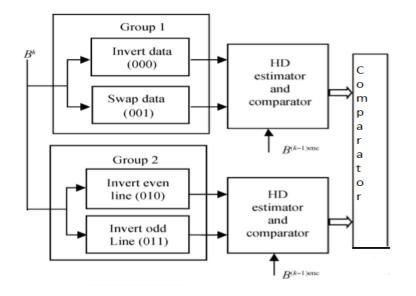

Fig 2 shows the module of the hardware which contains three blocks as follow:

- Multi-coding

- Comparator

- HD-estimator

Fig 2 Block diagram of technique based on multi-coded encoder

## 3.1 THE MULTI-CODING TECHNIQUE

In this segment, the information is coded in four distinctive manners and pair into two. Each pair has dual coding system control bits which are used to join all coding procedure to recuperate the first information at decoder. There are four sorts of coding in particular

### (A) Invert data

- **1.** Find the Hamming distance for the given data and present bus.

- **2.** If the Hamming distance came more than n/2, set invert will be = 1, now next bus esteem equal to the upcoming data esteem.

- 3. If not then, suppose invert = 0, and assume the next bus esteem equal to the estimation of the next data

Example 01101011100 convert 10010100011

### (B) Swap data

In this section, we have done swap two adjacent bit. After then we have compared the bit Example 011010111000 convert 100101110100

### (C) Invert even

In this section we have inverted the bit of even position of the data after then we have checked the no of transition. No of transition either increased or decreased. Example 001101011100 convert 011000001001

### (D) Invert odd

In this section, we have inverted the bit of odd position of the data after then we have checked the no of transition. No of transition either increased or decreased Example 001101011100 convert 10111110110

### **3.2 The HD Estimator**

This model independently counts Hamming separation between preferred data and coded information. Every single coding strategy then analyzes which coding technique has base Hamming distance of previous output as for 0100111011. The minimum distance of the technique will be taken in account.

### **3.3. COMPARATOR**

Here we have used comparator to compare the Hamming distance for various strategies and discover the least among them. The data as input to this block is the encoded information further more with its bit portrayal and its relative Hamming distance. This section shows encoded information with minimum amount of transitions.

### 4. SIMULATION RESULT

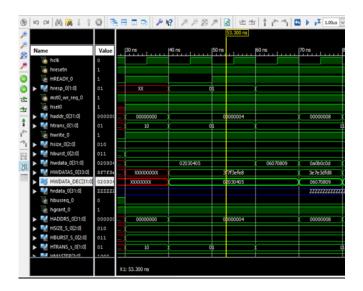

The simulation of the Proposed model is achieved with Verilog Xilinx , an HDL simulator as shown in waveform

Fig 3 Output waveform

Fig 4: Final Simulation waveform

| No of technique | Data       | Data xor previous output | Hamming distance |

|-----------------|------------|--------------------------|------------------|

| Invert data     | 0101000100 | 0001111111               | 7                |

| Swap data       | 1101000100 | 1001111111               | 8                |

| Invert even     | 0001011100 | 0101110111               | 7                |

| Invert odd      | 0010001000 | 0110110011               | 6(min)           |

|                 |            |                          |                  |

#### **Table 1** Minimum hamming distance

The results from the simulation figure show that the transfer of data from input to the out port takes the minimum vale. If we take care in account the hamming distance from the table 1it can be concluded that in case of invert data the distance is 7. When the swap data is calculated for hamming distance the it was 8. In invert even technique the hamming distance calculated as 7. The last one invert odd data the hamming distance calculated as 6. The minimum hamming distance of data calculated for the invert odd data. Fig. 5

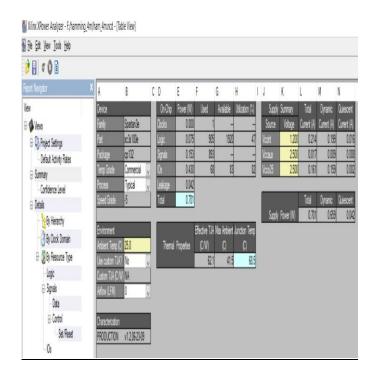

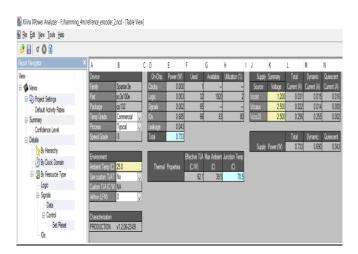

is an power estimator of hamming distance. The figure 6 is an power estimator of reference encoder .The idea behind this technique is by restricted move reduction in power .

#### Fig 5 Power of hamming distance estimator

**Fig 6** Power of reference encoder

### 5. CONCLUSION

The fundamental approach, in this paper, is to restrict the move action. The multi-coded procedure, 8-bit arbitrary information is coded in four conceivable approaches to limit the quantity of move action. This presented strategy is more compelling in diminishing power utilization. The power of the normal encoder is 0.690 and the intensity of the hamming distance estimator is 0.659. The overall power reduced is 0.031. The findings are simulated with HDL simulator Model-sim software and the power estimations are utilizing Xilinx. Furthermore, 1bit full adders are utilized in the Hamming distance calculator. The minimize number of transitions is a very good advantage of low power and area.

#### REFERENCES

- Alioto M, Palumbo G, Poli M. Energy consumption in RC tree circuits. IEEE Trans Very Large-Scale Integration (VLSI) Syst, 2006,14(5):452

- [2] Xie L, Qiu P, Qiu Q. Partitioned bus coding for energy reduction. Asia and South Pacific Design Automation Conference, 2005: 1280

- [3] "AMBA Specification Rev 2.0. ARM Ltd", 1999

- [4] Yu-Jung Huang, Ching-Mai Ko, and Hsien-Chiao Teng "Design and Performance Analysis of A Reconfigurable Arbiter", ISSN: 1109-9445 Issue 4, Volume 5, April 2008

- [5] M. R. Stan and W. P. Burleson, "Bus-invert coding for low-power I/O," IEEE Transactions On VLSI Systems, Vol.3, No.1, pp.49-58, 1995

- [6] Kumar A, Goyal A K. Study of various full adders using tanner EDA tool. International Journal of Computer Science and Technology, 2012,3:581

- [7] Rohit Hardia, Prof. Jai Karan Singh, Prof. Mukesh Tiwari "Design And Simulation of a typical high performance AHB Reconfigurable Master For On-chip bus Architecture using Verilog HDL", International Conference on Communication Systems and Network Technologies, IEEE 2011.

- [8] Pravin S. Shete, Dr. Shruti Oza "Design of an AMBA AHB Reconfigurable Arbiter for On-chip Bus Architecture" International Journal of Application or Innovation in Engineering & Management (IJAIEM) Volume 3, Issue 5, May 2014

- [9] Rishabh Singh Kurmi and Shruti Bhargava, "Design of AHB Protocol Block for Advanced Microcontrollers", International Journal of Computer Applications (0975 – 8887) Volume 32– No.8, October 2011, Page 23-29

- [10] K. Goossens, O. P. Gangwal, J. Rover, and A. P. Niranjan, "Interconnect and memory organization in SOCs for advanced settop boxes and TV – evolution, analysis, and trends", in J. Nurmi, H. Tenhunen, J. Isoaho, and A. Jantsch, Editors, Interconnect-Centric Design for Advanced SoC and NoC, Chapter 15, pp. 399–423, Kluwer, 2004.

- [11]H. Kopetz and G. Bauer. The time-triggered architecture. Proceedings of the IEEE, 91(1):112–126, 2003